Application Note

March 7, 2008

AN1220.1

# Using the Evaluation Board

The ISL6443 is a high performance triple-output controller offering control and protection features for 2 synchronous buck PWMs and 1 linear regulator.

The ISL6443 evaluation board highlights the operation of the IC in an embedded DC/DC converter application. Table 1 shows the available evaluation board.

**TABLE 1. EVALUATION BOARDS**

| BOARD NAME    | IC         | PACKAGE   |  |

|---------------|------------|-----------|--|

| ISL6443EVAL2Z | ISL6443IRZ | 28 Ld QFN |  |

## Recommended Test Equipment

- · A 12V, 5A capable power supply

- · An electronic load

- · Four channel oscilloscope with probes

- Precision digital multimeters

### Power and Load Connections

## Input Voltage

To connect a +12V power supply to the evaluation board, connect the positive lead of the power supply to the VIN (P1) post and the ground lead of the supply to the GND (P2) post.

The input voltage to the linear controller is already taken from the 1.8V output of  $V_{OUT2}$ .

## **Output Adjustment**

Change the respective output voltage feedback resistors to modify the output voltage using Equation 1:

$$V_{OUT1} = 0.8 \cdot \left(1 + \frac{R_1}{R_2}\right) \qquad V_{OUT2} = 0.8 \cdot \left(1 + \frac{R_3}{R_4}\right)$$

$$V_{OUT3} = 0.8 \cdot \left(1 + \frac{R_6}{R_{11}}\right) \qquad (EQ. 1)$$

## Soft-Start and Shutdown

The soft-start capacitors can be adjusted for sequencing of the output voltages, PWM start-up tracking, and/or to adjust the start-up current required to charge the output capacitors.

$$t_{\text{SS(PWM1)}} = C_2 \cdot \frac{0.8 \text{V}}{5 \mu \text{A}} \qquad \qquad t_{\text{SS(PWM2)}} = C_3 \cdot \frac{0.8 \text{V}}{5 \mu \text{A}}$$

(EQ. 2)

To independently shutdown the PWMs, the SD1 or SD2 pin can be pulled to GND using the on-board posts, P9 and P10 respectively.

#### **Power Good**

When both PWMs are within ±10% of their set value and the linear regulator output is within 75% of its set value, the PGOOD signal will go high. The open drain PGOOD pin is pulled HIGH to VCC\_5V on the board. The PGOOD circuitry monitors the FBx pin of each regulated output to determine if the outputs are in regulation. PGOOD can be monitored at post P8.

#### **Overcurrent Protection**

The overcurrent thresholds can be adjusted on the ISL6443 evaluation board. The current sense resistors, I<sub>SENSE</sub>, are set at  $1.0 \mathrm{k}\Omega$ . The overcurrent set resistor is 95.3k $\Omega$ . The overcurrent trip point can be adjusted by modifying R<sub>OCSET</sub>, R<sub>5</sub> and R<sub>10</sub>:

$$R_{OCSET} = \frac{7 \cdot R_{CS}}{I_{OC} \cdot r_{DS(ON)}}$$

(EQ. 3)

$R_{OCSET}$  is the overcurrent set resistor,  $R_{CS}$  is the current sense resistor,  $I_{OC}$  is the desired overcurrent trip point, and  $r_{DS(ON)}$  is the ON-resistance of the respective PWM's lower MOSFET. Refer to the ISL6443 Data Sheet for more information on how to select the current sense and overcurrent select resistors.

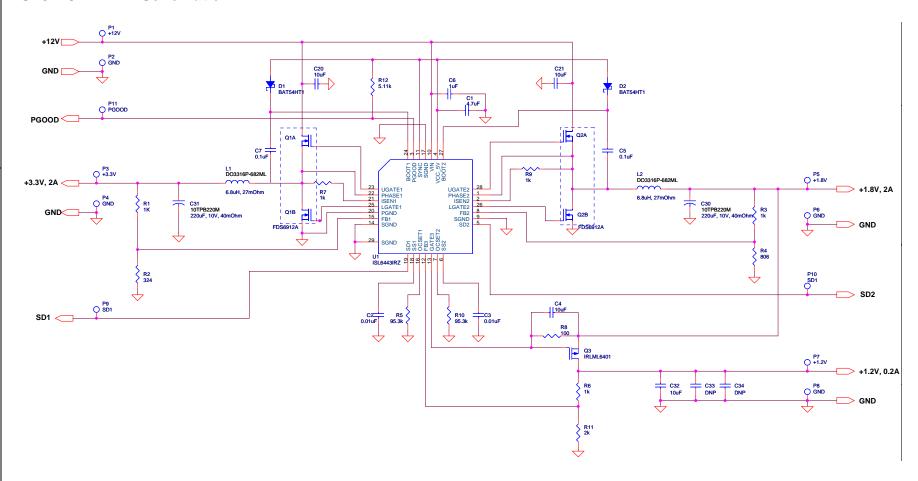

# ISL6443EVAL2Z Schematic

## ISL6443EVAL2Z Bill of Materials

| ITEM | REFERENCE          | QTY | PART NUMBER     | PART TYPE                      | DESCRIPTION             | VENDOR    |

|------|--------------------|-----|-----------------|--------------------------------|-------------------------|-----------|

| 1    | P1 to P12          | 12  | 1514-2          | Test Point                     | Turret 0.281 Height     | Keystone  |

| 2    | D1, D2             | 2   | BAT54HT1G       | Diode, Schottky                | 30V, 200mA              | On Semi   |

| 3    | C4                 | 1   | C1608X5R0J106   | Cap, Ceramic, X5R              | 10μF, 6.3V, 0603, X5R   | TDK       |

| 4    | C30, C31           | 2   | 10TPB220M       | Cap, POSCAP                    | 220µF, 10V              | Panasonic |

| 5    | C20, C21           | 2   | C3225X5R1C106KT | Cap, Ceramic, 1210             | 10μF, 16V, 1210, X5R    | TDK       |

| 6    | L1, L2             | 2   | DO3316P-682ML   | SMT Power Inductor             | 6.8μH, ±20%, 4.6A, 27mΩ | Coilcraft |

| 7    | C1                 | 1   |                 | Capacitor, Ceramic, 0603       | 4.7µF, 20%, 6.3V, 0603  | Generic   |

| 8    | Q1, Q2             | 2   | FDS6912A        | Dual NFET                      | 6A, 30V, Dual NFET, SO8 | Fairchild |

| 9    | C5, C7             | 2   |                 | Cap, Ceramic, 0603             | 0.1μF, 10%, 16V         | Generic   |

|      | C2, C3             | 2   |                 | Cap, Ceramic, 0603             | 0.01μF, 10%, 16V        | Generic   |

| 10   | C6                 | 1   |                 | Cap, Ceramic, 0603             | 1.0µF, 10%, 16V         | Generic   |

| 11   | C32                | 1   |                 | Cap, Ceramic, 0805             | 10μF, 10%, 6.3V         | Generic   |

| 12   | C33, C34           | 2   |                 |                                | NOT POPULATED           | -         |

| 13   | R8                 | 1   |                 | Resistor, Film                 | 100Ω, 0603, 1%, 1/16W   | Any       |

| 14   | R1, R3, R6, R7, R9 | 5   |                 | Resistor, Film                 | 1kΩ, 0603, 1%, 1/16W    | Any       |

| 15   | R11                | 1   |                 | Resistor, Film                 | 2kΩ, 0603, 1%, 1/16W    | Any       |

| 16   | R2                 | 1   |                 | Resistor, Film                 | 324Ω, 0603, 1%, 1/16W   | Any       |

| 17   | R5, R10            | 1   |                 | Resistor, Film                 | 95.3kΩ, 0603, 1%, 1/16W | Any       |

| 18   | R12                | 1   |                 | Resistor, Film                 | 5.11kΩ, 0603, 1%, 1/16W | Any       |

| 19   | R4                 | 1   |                 | Resistor, Film                 | 806Ω, 0603, 1%, 1/16W   | Any       |

| 20   | Q3                 | 1   | IRLML6401PBF    | Single NFET                    | Power MOSFET            | IR        |

| 21   | U1                 | 1   | ISL6443IRZ      | 300kHz, Dual PWM<br>Controller |                         | Intersil  |

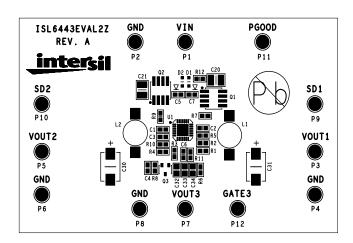

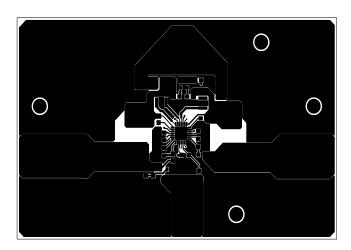

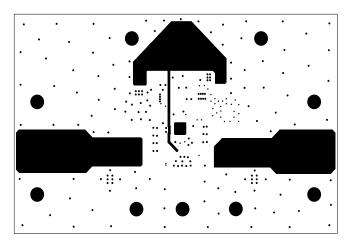

# ISL6443EVAL2Z Layout

FIGURE 1. TOP SILK

FIGURE 2. TOP LAYER

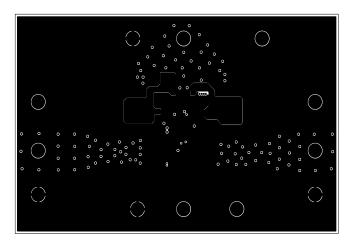

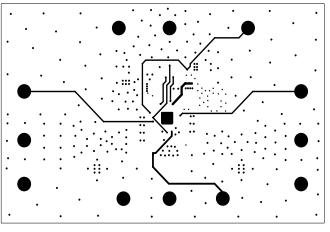

# ISL6443EVAL2Z Layout (Continued)

FIGURE 3. LAYER 2

FIGURE 4. LAYER 3

FIGURE 5. BOTTOM LAYER

FIGURE 6. BOTTOM SILK

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.